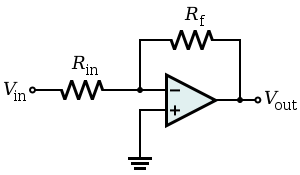

Negatif geri besleme kullanan op amp devreleri oluşturduğumuzda, şöyle:

... negatif geri besleme nedeniyle olduğunu varsayarak devreyi çok kolay bir şekilde analiz edebiliriz (aynı zamanda op amp'in ideal olduğunu varsayarsak, elbette).

Bu basitleştirilmiş modellerin çöktüğü bariz yüksek hassasiyetli durumların yanı sıra, bu ne zaman ve ne zaman geçerli değil?

Örneğin, geri besleme direncini başka bir elemanla değiştirirsek - belki bir kapasitör, indüktör, diyot (normal silikon diyot, zener diyot, vb.) Veya bunların ve diğer ortak devre elemanlarının bazı kombinasyonları - bunun nerede olduğunu nasıl biliyoruz? basitleştirme geçerli mi?

Ayrıca, direnç çok, çok yüksek hale geldiğinden, bir geri besleme elemanı olarak bir dirençle kalsak bile, bir noktada bunu açık bir devre olarak düşünebiliriz ve bu model açıkça yol boyunca bir yere ayrılır.

Yani, soru şudur: Bu yaklaşım hangi kısıtlamalar altında yararlı sonuçlar verecek "yeterince doğru"?

DÜZENLE:

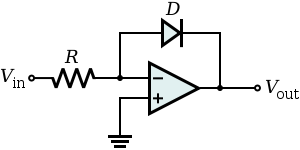

Başka bir örnek için temel eviren log amplifikatör devresini düşünün:

Shockley diyot denklemini çözersek

vD için, (üstel oldukça büyük olacağı için çoğunlukla alakasız olan 1'i yok )

Daha sonra olduğunu görmek için sanal kısa yöntemi kullanırsak , çıktı için doğru ifadeyi alırız:

Yani, sanal kısa yöntem burada çalışır. Ancak olduğunda bu diyot açık bir devre olacağından, analizin geçerli olacağını önceden nasıl anlayacağımı bilmiyorum .

+ve-terminalleri op-amp'in bir devrede kullanılmasından bağımsız olacaktır.